教程

根据慕课平台上提供的教程文档按步骤操作

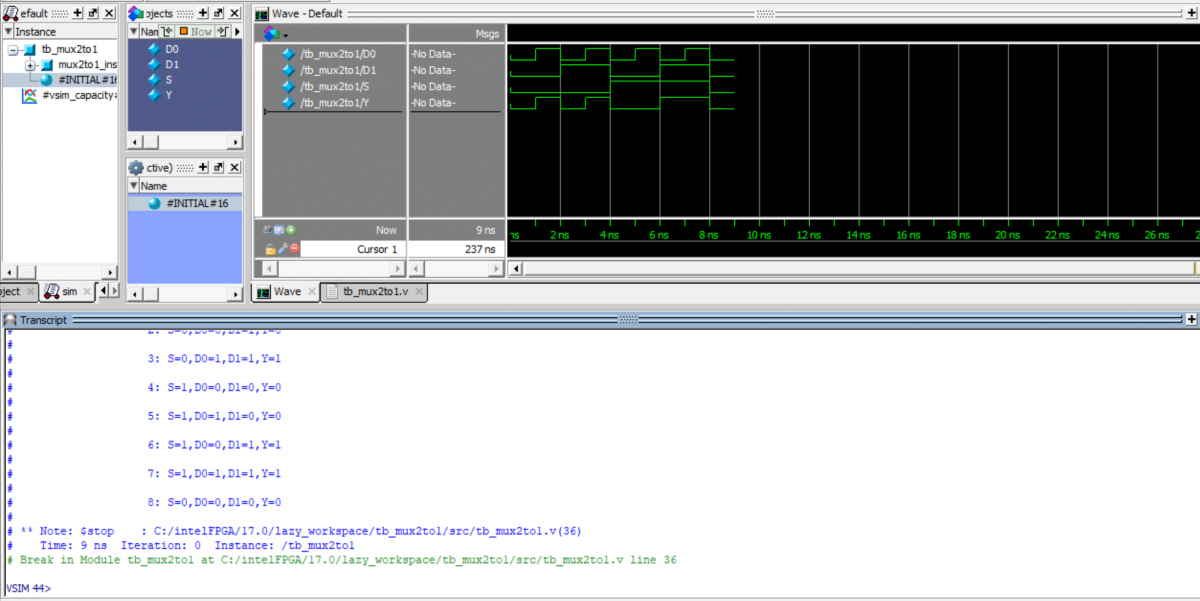

进行二选一数据选择器的设计与仿真:

一定要搞明白缩写系列:

mux为multiplexer的缩写

multiplexer:指多路复用器。是从两个或多个源(2的次方)到一单个信道。与数据选择器的概念一致

设计解读

- module是定义模[……]

锁存器的功能:实现对某一状态值的存储。

对于题目中的SR型锁存器,有两个输入端对存储的状态值进行设定,其中,只有Set有效时,存储的状态值Q被置为1;只有Reset有效时,Q被置为0.

对于S和R同时有效(为1)的情况,由于或非门G1、G2对1敏感——只要有1[……]

6.15更新:老师公布讲解视频后的一些思路整理

4.25全篇完成[……]

奇校验码:信息位和校验位 1 的个数为奇数

解析见下页:

两道题相互补充,列逻辑电路真值表:

AB C D L1L2L00000001000101110000011100111111000 ……

符[……]