教程

根据慕课平台上提供的教程文档按步骤操作

进行二选一数据选择器的设计与仿真:

一定要搞明白缩写系列:

mux为multiplexer的缩写

multiplexer:指多路复用器。是从两个或多个源(2的次方)到一单个信道。与数据选择器的概念一致

设计解读

//file name: mux2to1.v

module mux2to1(

input D0, //输入信号 D0

input D1, //输入信号 D1

input S, //输入选择信号 S

output reg Y //输出信号 Y

);

/*电路功能描述

1.(*)表示 always 块中所有输入信号都是敏感信号

2.Y 必须定义成 reg 型

*/

//Y:2 选 1 数据选择器输出数据

always @(*)begin

//or: always @(D0 or D1 or S)

if(S == 1'b1)//or: if (S) Y = D1;

Y = D1;

else

Y = D0;

end

endmodule- module是定义模块开始的关键词,以endmodule结束

- input与output说明端口类型(信号流方向)

- 端口数据类型默认为wire

- 线网型:包括wire/wor/supply1/supply0/…

- 寄存器类型:包括reg/integer/real(time)/time

- 过程块语句结构包括initial和always两种

- 过程赋值语句只能给寄存器类型(包含reg)变量赋值,因此有上程序中提到的必须将输出Y设为reg类型

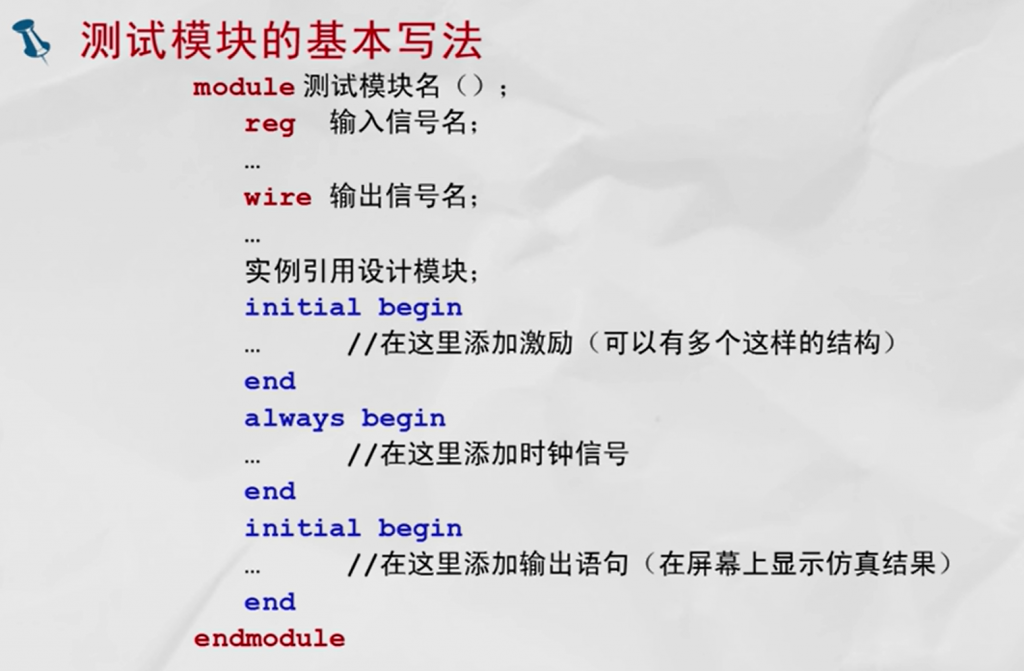

仿真解读

//file name:tb_mux2to1.v

`timescale 1ns/1ns //时间单位为 1ns,精确度为 1ns

module tb_mux2to1; //激励模块(顶层模块)没有端口列表

reg D0, D1, S; //声明输入信号

wire Y; //声明输出信号

//2选1数据选择器模块例化

mux2to1 mux2to1_inst(

.D0(D0),

.D1(D1),

.S(S),

.Y(Y)

);

initial

//打印到输出界面

$monitor($time,":\tS=%b,D0=%b,D1=%b,Y=%b\n",S,D0,D1,Y);

initial begin

//初始化

S = 0; D1 = 0; D0 = 0;

#1

S = 0; D1 = 0; D0 = 1;

#1

S = 0; D1 = 1; D0 = 0;

#1

S = 0; D1 = 1; D0 = 1;

#1

S = 1; D1 = 0; D0 = 0;

#1

S = 1; D1 = 0; D0 = 1;

#1

S = 1; D1 = 1; D0 = 0;

#1

S = 1; D1 = 1; D0 = 1;

#1

S = 0; D1 = 0; D0 = 0;

#1

$stop;

end

endmodule

- 信号类型

- 输入用reg:保持输入信号不变

- 输出用wire:随时监测输出信号的变化

- 时间线

- `timescale 1ns/1ns为编译器语句,进行仿真的总设置

- initial代表从初始时间0s开始,每个initial语句段平行

- #1代表延时1s

- 交互语句

- $stop;停止仿真不退出,可以继续run

- $finish;退出仿真

- $monitor()编译器窗口输出内容

- $time执行语句当前时间

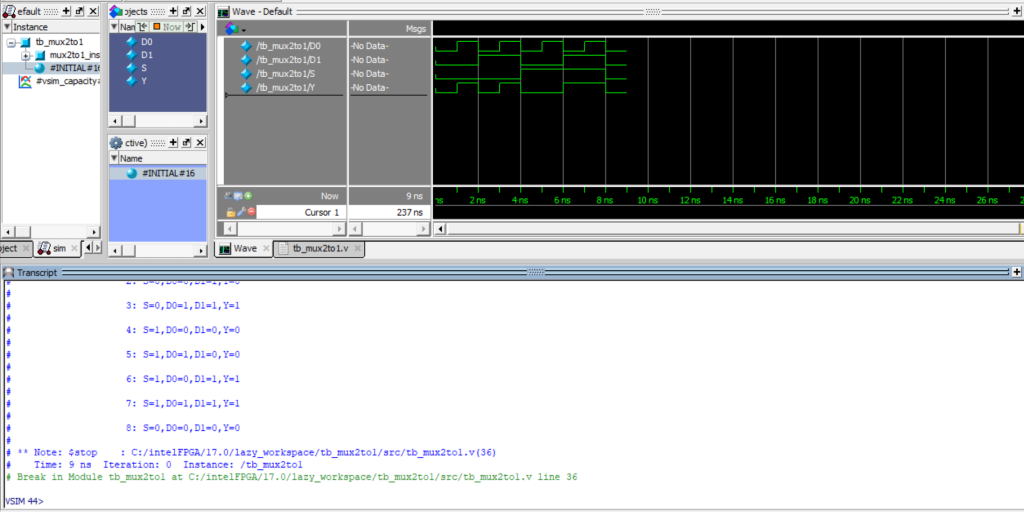

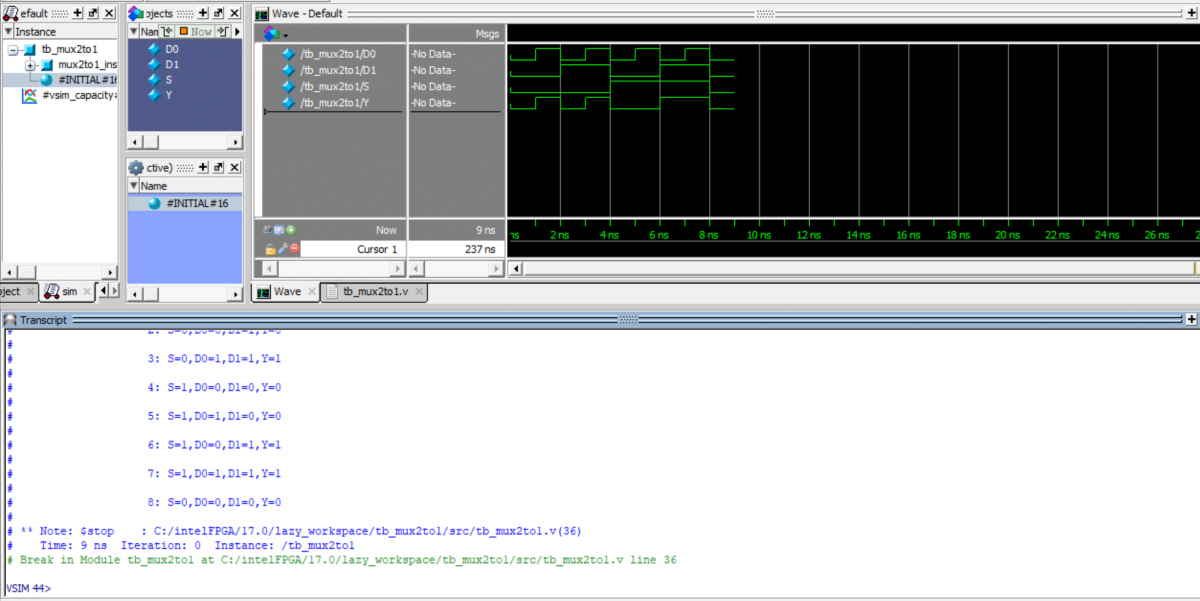

结果图