一、由555定时器、3-8线译码器74HC138和4位二进制加法器

74LVC161组成的时序信号产生电路如图所示。

- 试问555定时器组成的是什么功能电路?

- 试问74LVC161组成什么功能电路?列出其状态表;

- 画出图中v。1、Q3、Q2、Q1 Q, 及L的波形。

多谐振荡电路

555定时器的这种连接方式为多谐振荡电路,其中有:

(1) ![]()

(2) ![]()

即高电平脉宽为低电平脉宽的2倍

计数器

74HC161采用反馈置数法组成模数为5的计数器,状态表为

| Qn | Qn+1 |

| 1011 | 1100 |

| 1100 | 1101 |

| 1101 | 1110 |

| 1110 | 1111 |

| 1111 | 1011 |

对于74HC138译码器组成的输出电路部分,L为有效Y的相或

(3) ![]()

即:

(4) ![]()

波形图

仿真程序

//filename:general1.v

`timescale 1ns/1ns

module general1;

reg CR_n,EN,CP;

reg [3:0] D;

wire [3:0] Q;

wire TC,PE_n;

supply0 GND;

supply1 VCC;

wire [7:0] Y_n;

wire L;

//实例化调用反馈置数法的X模制计数器

//调用计数器74LVC161

counter_161 U1(

.CR_n(CR_n),

.PE_n(PE_n),

.CEP(VCC),

.CET(VCC),

.CP(CP),

.D(D),

.Q(Q),

.TC(TC)

);

//实例化74X138

decoder74X138 U2(

.E1_n(GND),

.E2_n(GND),

.E3(Q[3]),

.A(Q[2:0]),

.Y_n(Y_n)

);

//输出

assign L=~(Y_n[3]&Y_n[5]&Y_n[6]);

//计数最高则置数端有效

assign PE_n=~TC;

initial begin

EN<=1;

CP<=0;

D<=4'B1011;

end

//产生时钟信号

always begin

#1

CP=~CP;

#2

CP=~CP;

end

initial begin

#1//清零

CR_n<=0;

#1

CR_n<=1;

#80

$stop;

end

endmodule

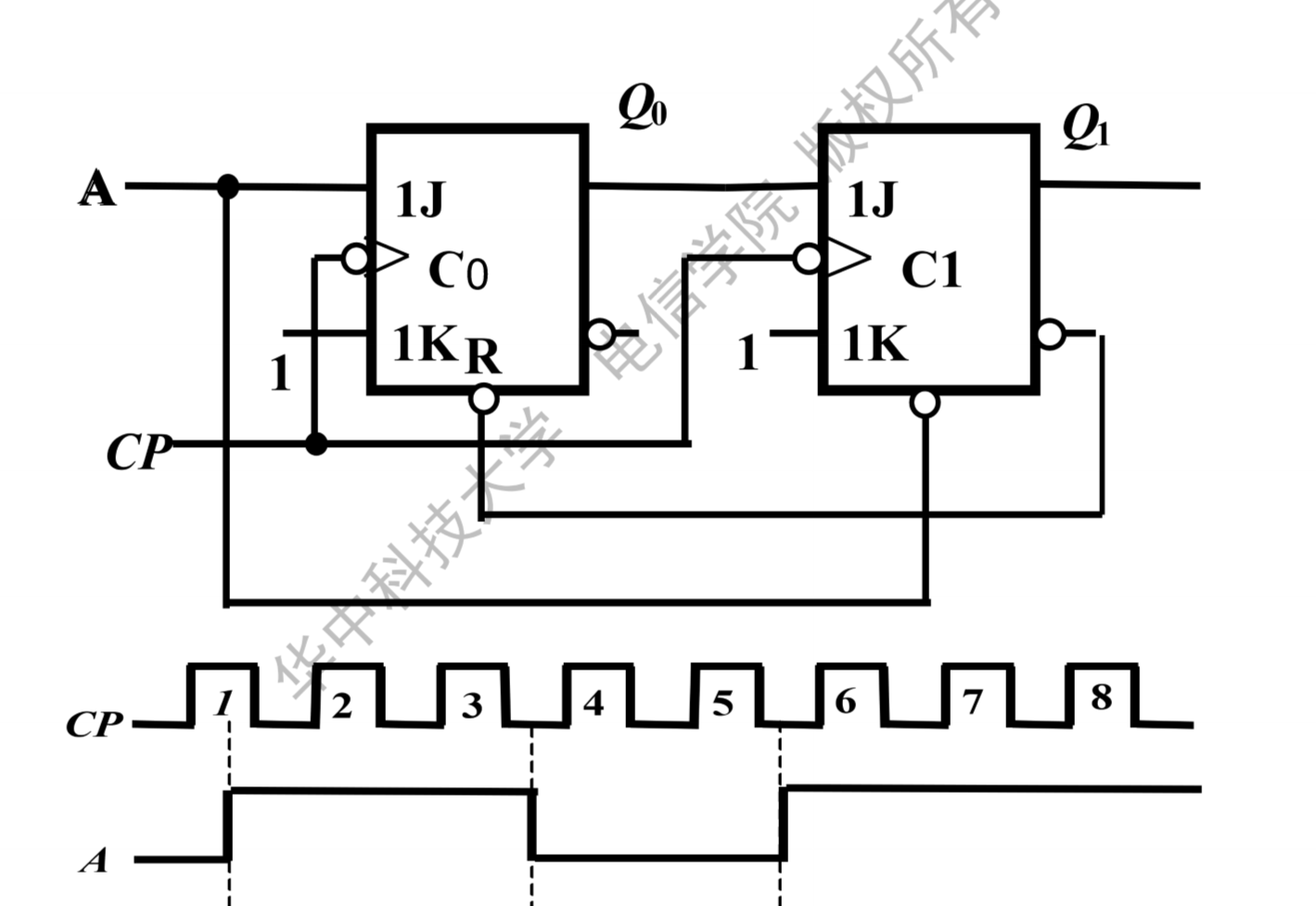

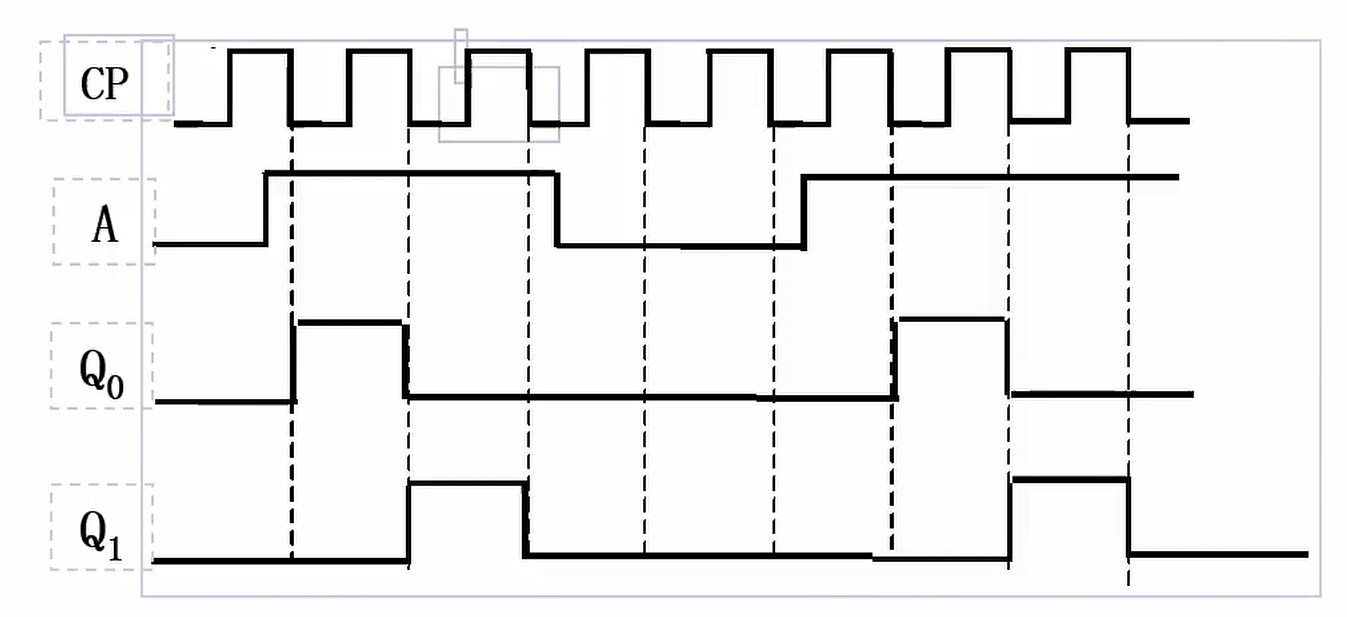

二、时序电路如下图所示,已知A、CP的波形,试对应画出Q1、Q0输出波形。(假设电路的初态为00)

注意:

本题的触发器C0具有异步清零端,即Q1n为1时,Q0n+1为0

方程

状态转换表

| Q1n(R0)Q0n | A=0 | A=1 |

| 00 | 00 | 01 |

| 01 | 10 | 10 |

| 10 | 00 | 00 |

| 11 | 00 | 00 |

输出波形

三、集成移位寄存器74HC194和10位集成D/A转换器AD7533组成的电路如图六所示,已知CP和ST的波形:

- 试画出QD、Qc QB、QA的波形;

- 定量出画图中vO的波形;

- 已知CP的频率f=1KHz,试确定vO的周期。

注意:

该寄存器A为最高位,而D为最低位

寄存器部分

- 74LS194是四位双向通用移位寄存器。移位的方向,右移(方向是QA到QD),左移(方向是QD到QA)。左移是高位到低位。

- 寄存器的S0一直为H

- 当ST为L时,S1为H,则寄存器功能为将DCBA数据移至输出。时钟脉冲上升沿到来,Q为1110

- 此后ST为H,Q中有0项,经过与非门为H,则S1为L,寄存器功能为右移,右移数据为QD =1,一次时钟脉冲上升沿时,Q为1101,之后为1011、0111、1110,开始循环

D/A转换部分

Q输出由DBCA分别对应D/A转换器的D输入6789,公式:

(5) ![]()

则1110对应:

(6) ![]()

(7) ![]()

同理,1101对应-6.5V,1011对应-5.5V,0111对应-3.5V:

vo的周期即Q循环一次的周期,为时钟周期的4倍,即:

(8) ![]()

四、图示为四选一多路器。图中A1为地址选择端最高位,D3为数据输入端最高位,W为输出。输入输出均为高电平有效。该电路所实现的函数表达式为

五、利用ROM构成的任意波形发生器如图题7.1.5所示,改变ROM的内容,即可改变输出波形。当ROM的内容如表题7.1.5所示时,画出输出端随CP变化的波形。

输出表达式

(9) ![]()

(10) ![]()

(11) ![]()

(12) ![]()

(13) ![]()

(14) ![]()

波形图

六、计数型A/D转换器的原理电路如图所示,A为比较器,当Vi大于Vo时输出为1,当Vi小于Vo时输 出为0; CR为低电平有效的清零信号,每次转换前CR信号都将计数器清零; Vr为高电平有效的转换控制信号,CP为时钟信号,频率为100KHz;计数器模块为8位二进制加法计数。

- 请说明该电路实现A/D转换的原理。

- 完成一次A/D转换的最长时间为多少?

- 若8位D/A最高可输出Vomax=9.18V,当Vi= 5.410V时,电路输出结果的值为多少?此次转换的时间为多少?

- 在计数器的作用下,改变Vo为不同权值电压。通过电压比较器,将输入电压Vi不同权值的电压Vo进行比较,得到转换的数字量。

- 最长时间即从最高权值一直比较到最低权值得到结果,即进行8位的比较,需要8个时钟脉冲:Tmax=8*Tcp=0.08ms

- 第一位为2^7/(2^8-1)*9.18=4.608,依次类推得到之后每位的权值为2.304、1.152、0.576……

- 通过输出逐次比较,最终结果为10010110

- 转换时间为0.08ms

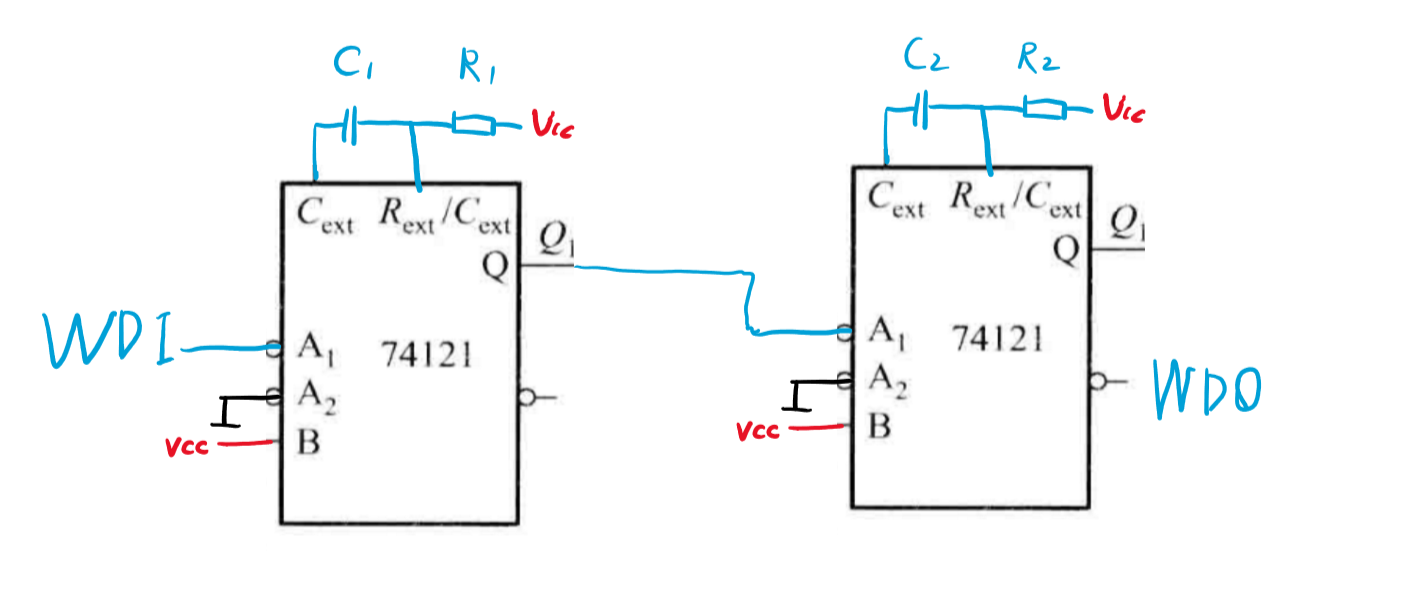

七、下图即为采用全数字方式实现的看门狗定时电路,其中OSC为多谐振荡器。请简要说明电路工作原理,并指出一次触发产生的最大高电平定时脉宽和WD0输出的复位信号宽度。若采用单稳触发器来实现该功能,画出电路图

工作原理

OSC多谐振荡器产生矩形脉冲,做为10Hz的时钟信号传入计数器74HC161.

当计数器到达最高位数1111时,产生进位信号,TC有效,则WD0经非门后输出为低电平,分别

- 传递至计数器的预置信号PE为有效低电平,等待下次时钟脉冲时,置位为0000

- 传递至D触发器的复位端R,使输出Q为低电平,并传递至计数器的使能端CEP,计数无效

最大高电平定时脉宽

当输入信号WDI为下降沿时,传递至计数器CR为有效低电平,计数器清零。

当输入信号WDI为上升沿时,将D的值传递至计数器使能端CEP,计数器开始在OSC的脉冲下从0000开始计数,直至计至最大值1111使进位端TC为高电平,最大高电平定时脉宽即TC低电平持续时间,为15个时钟信号周期,即1.5s

WDO复位信号宽度

即WDO为低电平保持时间,等同于TC高电平保持时间。根据74HC161功能可知,为一个时钟信号周期,即1/10Hz=0.1s

单稳态触发器实现

由暂稳态持续高电平时长公式为T=0.7RC,通过调制R和C的大小实现电路功能

如,取R=2kΩ,C=0.1mF,T=0.14s

根据上述分析,在输入信号WDI有效后,电路输出WDO分别需要维持特定T1时长的高电平后,再下降为低电平保持T2时间再恢复高电平,则需要两个单稳态触发器分别记录两段时间

由于高电平定时脉宽是从WDI上升沿开始计时,则第一个单稳态触发器的触发沿选择上升沿;而低电平是在高电平持续结束后开始,则选择第二个单稳态触发器的触发沿为下降沿。

对于T1=1.5s,T2=0.1s,不妨取C1=C2=100μF,则R1≈21.4kΩ,R2≈1.4kΩ